4bit 加算器

加算器 減算器の原理 制御工学の基礎あれこれ

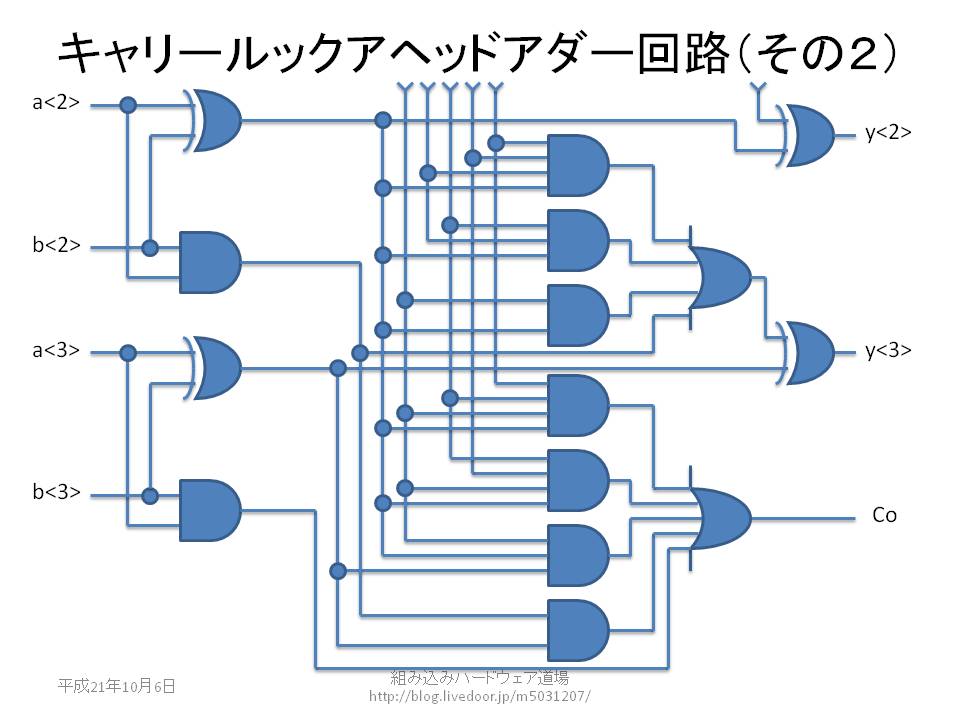

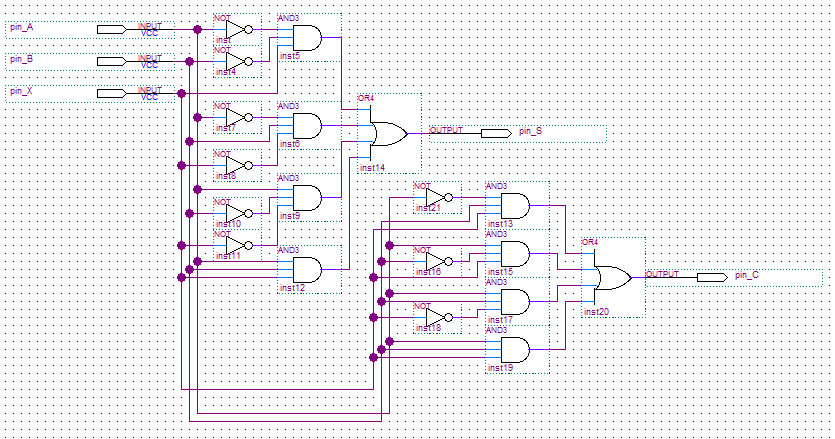

キャリールックアヘッドアダー回路 組み込みハードウェア道場

4bit全加算器 Oxygennotincluded Advanced Notes

加算器 その2 Kivantium活動日記

第2回

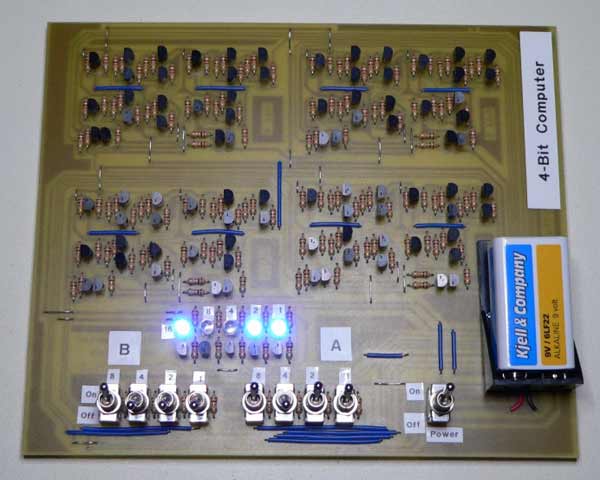

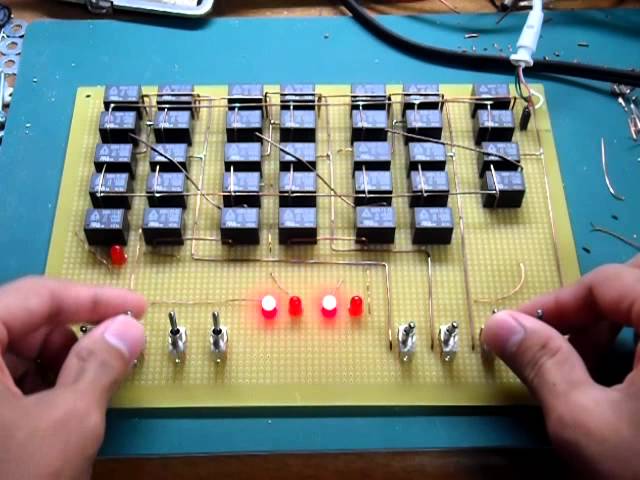

リレーによる 4bit 加算機

備忘録②の続き。 加算回路 半加算器 2進数の足し算は、 0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10 と書ける。これの足される数を入力a、足す数を入力b、その桁の加算結果を出力s、桁上りを出力coとして真理値表で示すと、以下のようになる。coは桁上りが生じたかどうかを表すビットであ….

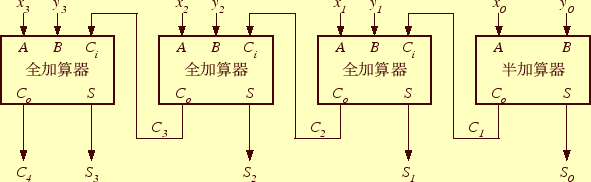

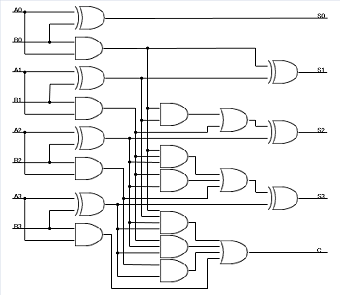

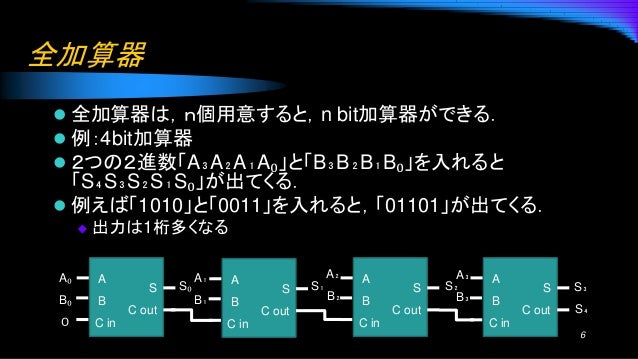

4bit 加算器. 全加算器を組み合わせて,複数ビットの加算をする論理回路を作る ★2.4.1 半加算器 半加算器(☆11) は,入力として2 つの1 ビットの数を受け取り,それらの和と上 ☆11) 英語でHalf Adder と いうので,HA と略記すること がある.. 課題2: 『自分の名前を表示させよう』の開発仕様 130. Bit拡張と数値演算 この記事はひとりでCPUとエミュレータとコンパイラを作る Advent Calendar 17の6日目の記事です。 昨日は変数(レジスタ)の数を4個に増やして、mov命令が実行できるCPUを設計した。 しかしmov命令だけでは大したことができない。 そこで今日は(浮動小数点を含む)四則演算がで….

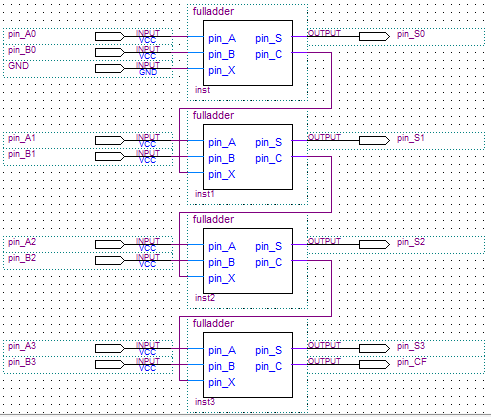

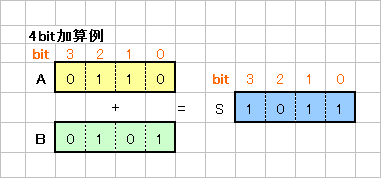

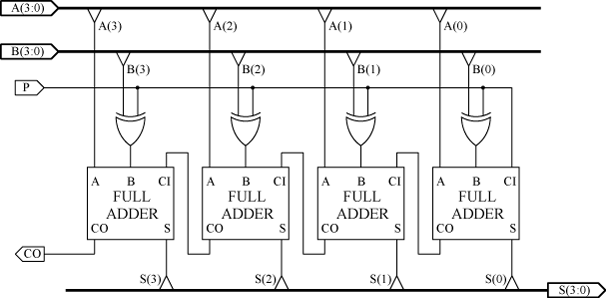

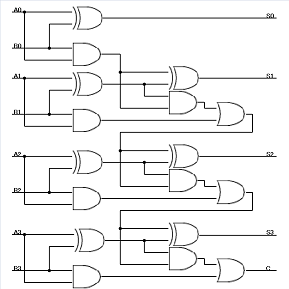

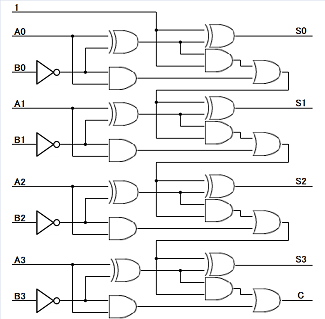

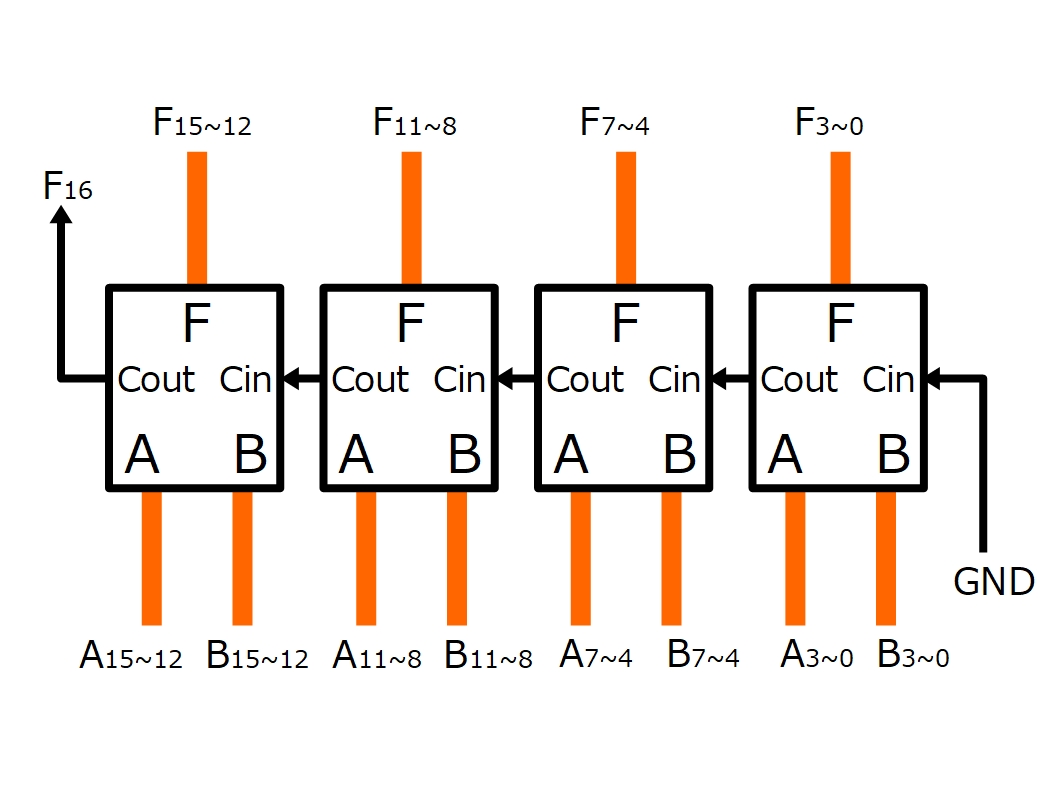

その結果繰り上がりが生じた場合は、さらに上位の加算器へと入力を行うという処理が何度も続いていくのである。 4bit加算器の例(0101 + 1110 = ) 上の回路を4つ接続することによって、4bitの加算器を作ることができる(下図)。. リレー式 4Bit加算器 ニコニコ技術部 高校の文化祭で展示したら誰も説明を見ず「何コレー」カチカチ で終わったのでココに展示XORとANDの半加. 4bit加算器と聞くと学生の時にやったという方もおられるかと思います。 加算器というのは2進数の足し算を行う回路の事です。 今回はそれを4bit分接続したものになります。 最もシンプルな加算器は以下の図の回路です。.

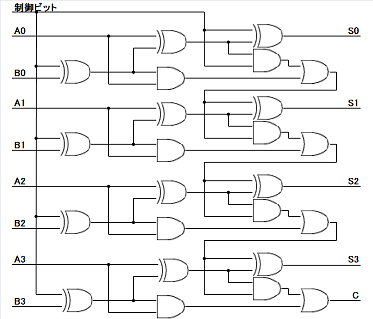

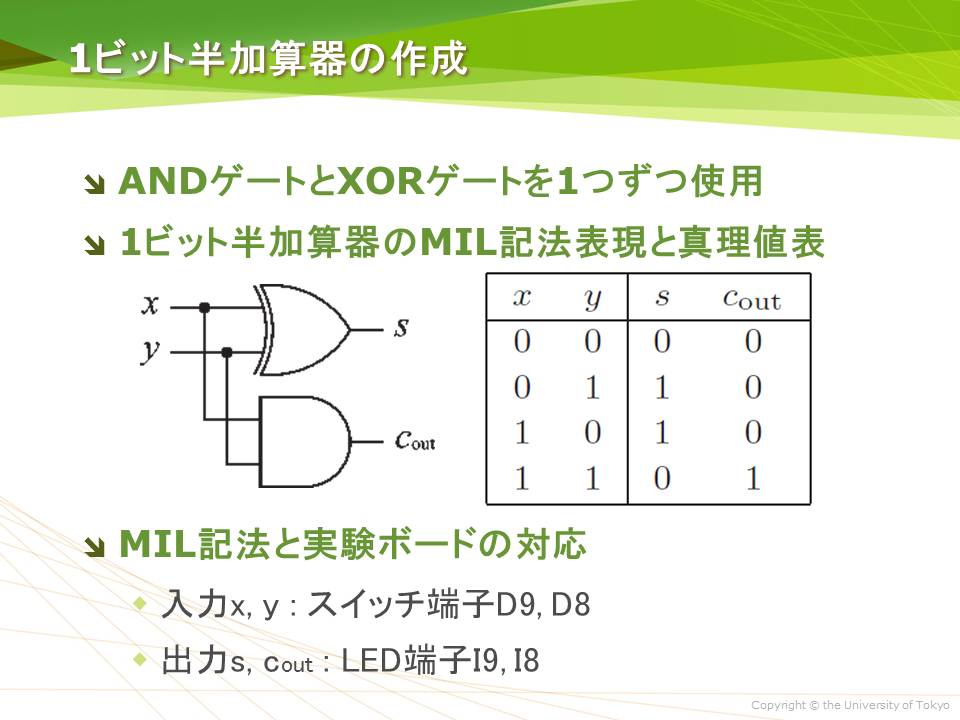

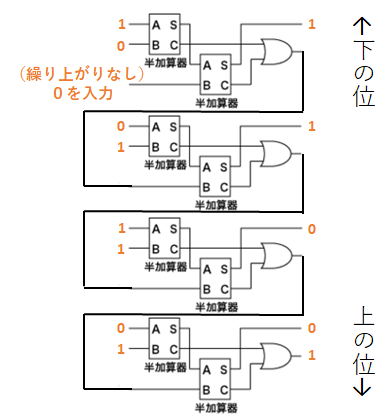

今回からは論理回路を使って計算(加算)を行うことについて考える。まずは手始めに、1bitの加算を行う。 半加算器(1bit加算器) 1bitは0と1を表現できるため、1bitどうしの加算には以下の4パターンがある。 0 + 0 = 0 (2進数:00) 0 + 1 = 1 (2進数:01). 簡単な4ビットALUの設計 ALUとは何か • ALUとはArithmetic Logic Unitで略で、算術論理演算器とも言われる。 • 通常ALUはマイクロプロセッサの内部で使用され、データに対して加算、引き 算、論理和、論理積などの種々の算術論理演算を行う。 • 基本的にALUは単なる組み合わせ回路である。. ここからは、これまでのゲート回路を使いつつ、4bit 加算器をより単純な部品から組み立てていくことにしましょう。4bit 加算器は、半加算器と全加算器という部品に分解することができます。 半加算器 - Wikipedia;.

この記事はkivantium Advent Calendarの7日目です。昨日は乗算器の準備のために順序回路の構成要素であるラッチとフリップフロップについて簡単に触れ、シフトレジスタを導入しました。今日は掛け算を行う回路を作っていこうと思います。 単純な符号なし乗算器 その1 掛け算の基本的考え方は筆算. (4) 4ビット加算器 (adder) の記述例(2) 上の例では、半加算器と全加算器を組み合わせて、4bitの加算回路を設計しました。 一方、 VHDL には、 算術演算 やICの74シリーズに相当する機能を実現するマクロ、メモリ関連など、. この記事はkivantium Advent Calendarの3日目です。昨日はNANDゲートから任意のゲートを作れることを確認しました。 ここからは何回かに分けて四則演算などの基本的な計算を行う回路の実現方法を書いていきます。四則演算は組み合わせ回路として書けるので、NANDであらゆるゲートを作れる以上実現.

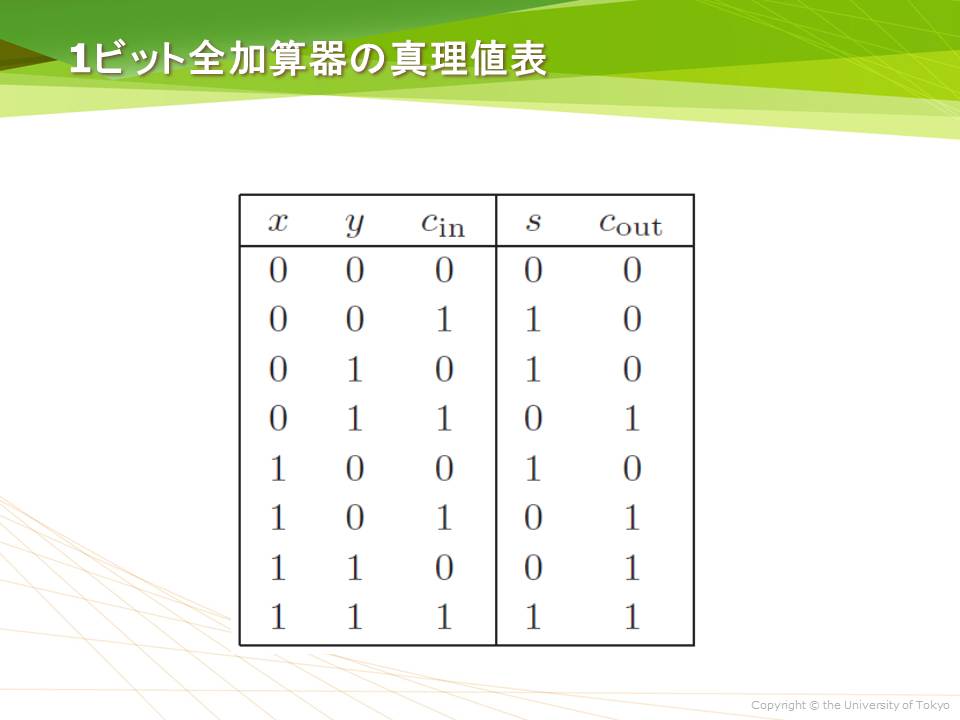

全加算器をn 個を直列に接続してc0 に 0 を入力するという構成もある (c0 に1 を入力すると, s = a+b+1 が計算される) FA co s a b ci FA co s a b ci FA co s a b ci FA co s a b ci a3 b3 a2 b2 a1 b1 a0 b0 c4 s3 s2 s1 s0 c3 c2 c1 c0=0 • 半加算器の真理値表とゲートによる設計例. 従来方式(デジタル乗算器)の問題点 15/9/14 回路規模・消費電力・演算時間が大 部分積&加算のため全加算器の2次元配列 例:8bit×8bit の場合 直接的構成では8×8=64個の全加算器が必要. そのままデジタル値を受けて動作する回路方式をバイナリ方式と呼びます。 抵抗使用の場合のバイナリ方式は、回路構成によりデータに重み付けを持たせたもので、代表例としてr-2rラダー回路があります。 キャパシタ使用の場合のdacは、スイッチを切り替えながら.

5 (0101) の2 の補数(4ビット) 16-5 = 11(1011) ①全てのビットを反転させる ②1 を加える 0101 1010 1011 ①. 2.4.加算回路の設計 1).1Bit どうし(2Bit)の加算回路(半加算回路) 加算回路 A B S (和) C (桁上げ) 1Bit 加算回路のイメージ図 1Bit の加算例 0+0= 00 0+1= 01 1+0= 01 1+1=10 桁上がり 1Bit の加算例をもとに真理値表を作成する。 1Bit 加算の真理値表. 加算器 x1 x0 ci s3 s2 co fa4 x3 x2 y1 y0 y3 y2 s1 s0 fa x y co ci s fa x y co ci s fa x y co ci s fa x y co ci s x y co s fa ci 減算 • 除数を2 の補数に変換してから加算 x の2 の補数:.

And, or, ex-or ゲートを用いて半加算器,および,全加算器のそれぞれを 1つ構成し, それらを組み合わせて,2進2ビットの加算回路を作成せよ. 作成した回路はシミュレーションにより動作を確認すること.. 4bit加算器と聞くと学生の時にやったという方もおられるかと思います。 加算器というのは2進数の足し算を行う回路の事です。 今回はそれを4bit分接続したものになります。 最もシンプルな加算器は以下の図の回路です。. 4bit加算器と聞くと学生の時にやったという方もおられるかと思います。 加算器というのは2進数の足し算を行う回路の事です。 今回はそれを4bit分接続したものになります。 最もシンプルな加算器は以下の図の回路です。.

全加算器の論理式を変形する時に、どのような点を考慮して式を変形したか。 全加算器を半加算器 2 個と適当な論理演算の素子で構成する時の回路図を示しなさい。 全加算器への入力が a=0, b=1, c=1 のとき、s’ と s’c の値を求めなさい。. Logisimは、作った回路を部品として使えるので、上記半加算器にHAというラベルを付けて、それを元に1bitの全加算器を作りました。 全加算器 Full adder. 2 2ビット選択器 •22=4本の入力d 0,d1,d2,d3から1本を選択 –2ビット信号s =(s1,s0)で制御 d0 d1 d2 d3 q 制御信号s 入力 出力 s =0 s =1 s =2 s =3 ss1s0 q 00 0d0 10 1d1 21 0d2 31 1d3 2ビット選択器 di s1s0 q d0=0 0 0 0 d0=1 1 d1=0 0 1 0 d1=1 1 d2=0 1 0 0 d2=1 1 d3=0 1 1.

半加算器やリレーによる半加算器のページで、 基本論理回路やリレーを使えば、 半加算器を作れることが分かりました。 半加算器は 2 個の 2 進数の足し算ができます。 0 + 1 = 1、 1 + 1 = 10 などが計算できる 「賢い」 回路です。. 4ビット加算器は全加算器(full adder)と半加算器(half adder)を組み合わせることによって作成することができます。まずは、今回使用した半加算器と全加算器を見ていきましょう。 半加算器. 全加算器の二次元配列を用いた乗算器 回路規模・消費電力・演算時間が大 部分積&加算のため全加算器の2次元配列 例:8bit×8bit の場合 直接的構成では8×8=64個の全加算器が必要.

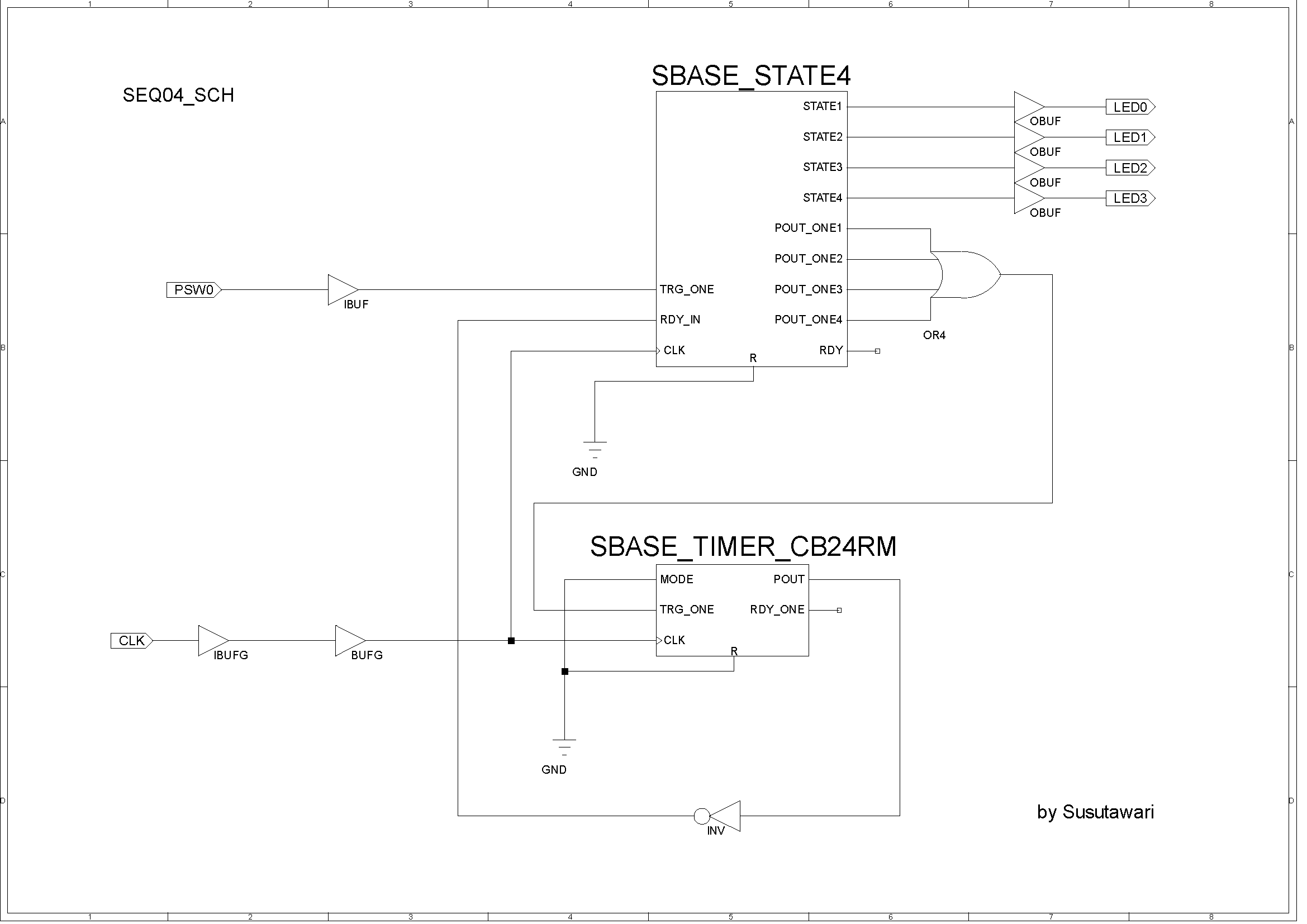

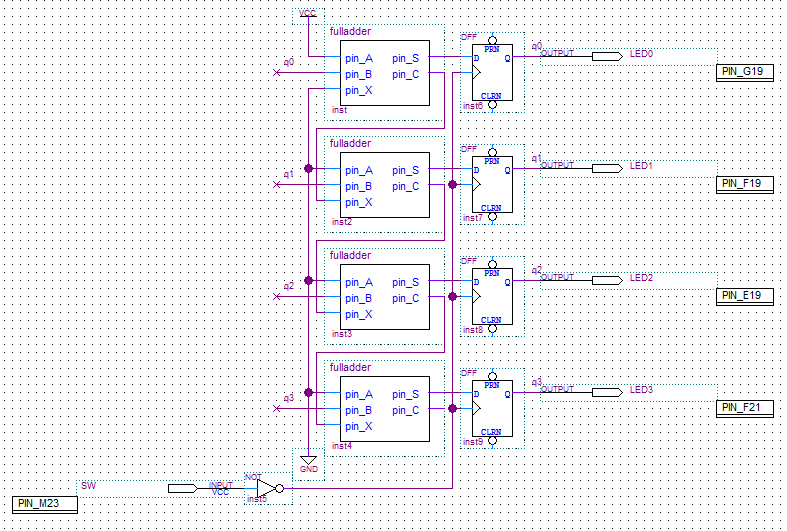

リプルキャリー方式加算器 3ビット加算器:入力( A1 A0), (B2 B1 B0) 出力(C2 S2 S1 S0) 上位桁に向かって順次桁上げし、加算を実行 ripple carry方式:水面に石を放り込んだときにさざ波 (ripple)が伝わるのに似ていることが語源 加算器の段数が増えると加算結果の. 電子回路ドリル III(2):問題2 4ビット加算器をVerilog HDLで記述しよう 回路は“モジュール”の枠に収めて定義し、信号は“ポート”として. データセレクタとROMから送られる4bitの入力を加算し、A~Dレジスタに出力します。 繰り上がりが発生した場合はキャリーフラグに'1'を出力しますが、これを分岐命令に利用します。 ALUは階層設計で作成します。 まず1個の全加算器のコードが以下です。.

下図はリレーで作った半加算器です。 図中、 はリレー a のコイルを表しています。 スイッチ a を on にすると、 電磁石の働きでリレー a の 3 つの接点 a が同時に動きます。 は接点 c - b を使っていますから、 スイッチ a を on にするとこの接点は off になります。. この加算器はFull Adderと呼ばれ、FAと略して記載します。 4bit加算器 半加算器と全加算器を組み合わせると桁が多くなっても計算することが出来ます。具体例として5+9の結果を示します。 減算器 減算器は加算器で表現することが出来ます。. 半加算器は入力(a,b)と出力(c,s)からなり、次のような真理値表になります。入力出力abc s000 0010 1100 1111 0この真理値表から、次….

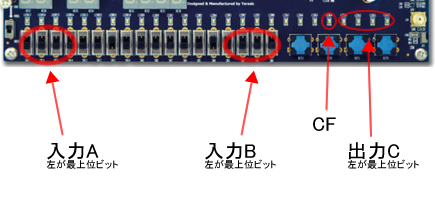

32ビット加算器の設計 1ビット加算器を使った32ビット加算器 + s31 a31 cout + + s1 s0 b31 b1 b0 a1 a0 cout cout cin 0 cin 下位から上位へ桁上げが伝播 ・・・ cout cin 順次桁上げ加算器 (ripple carry adder). 加算器によるオーバーフロー対策です。例えば4bit同士の加算を行うとき、 1001b(4bit) + 1110b(4bit) = b(5bit) のように1bit増える可能性があるため、あらかじめ1bit付加して加算を行う事で、オーバーフローによるエラーを防ぎます。. 4bitの2進数の加算回路は、1個の半加算器と3個の全加算器で構成することができます。 その回路構成を以下に示します。 2.4 7セグメントLED駆動用デコーダ回路回路.

加算器アダー / adder / 加算回路とは、一桁の2進数(一般的には2つの数の同じ桁同士)の加算を行う論理回路。2つ数の同じ桁同士を加算し、下からの繰り上がりを考慮しないものを半加算器、同じ桁同士と下位の桁からの繰り上がりの3つを加算するものを全加算器という。.

第2回

Portal2 二進数4ビット加算器を作ってみた Den Noguchi

Q Tbn 3aand9gctqaofgc9iq9umjkjkd8volwma I2agkom3gq Usqp Cau

加算器 Wikipedia

加算器 減算器の原理 制御工学の基礎あれこれ

リレーを使った4ビット2進加算器 Gijyutu Com 技術の面白教材集

Ie U Ryukyu Ac Jp Wada Digcir11 Digcirhandout7 Pdf

問題2 4ビット加算器をverilog Hdlで記述しよう Monoist

Test04 回路を部品化する にがてぶろぐ

6日目 Cpu Bit拡張と数値演算 しかくいさんかく

Schematic Entry 4 Bit Carry Look Ahead Adder

Http Www Ed Noda Tus Ac Jp Jte401 Files 19 Text 2 Pdf

リレーによる 4bit 加算回路

論理ゲートをpythonで作ってcpuを学ぶ 第1回 Qiita

リレーによる半加算器

リレーによる 4bit 加算機

リレー式 4bit加算器 Youtube

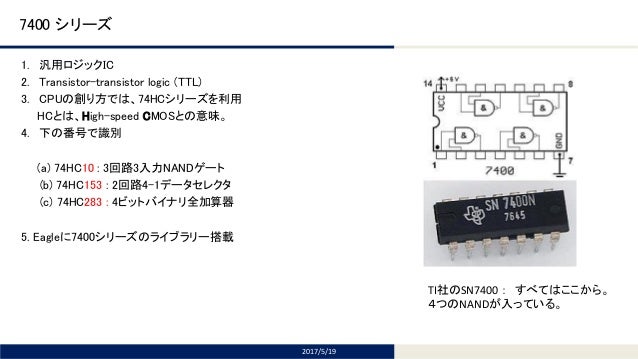

ttlでcpuを作ろう

論理回路シミュレータlogisimで加算回路 はじめてプログラム

1999 号 桁上げ先見回路および並列加算器 Astamuse

ハードウェア記述言語 その2

リレー式 4bit加算器 ニコニコ動画

4bit加算器 2 写真共有サイト フォト蔵

16 Bit Cellular Cla Adder Download Scientific Diagram

74hc2 74hc373 74hc253 74hc32

リレーを使った4ビット2進加算器 Gijyutu Com 技術の面白教材集

リレーによる 4bit 加算機

にがてぶろぐ

全加算器回路の真理値表から S Coをa B Cを使って Yahoo 知恵袋

四位计算机的原理及其实现 阮一峰的网络日志

リレーによる 4bit 加算回路

アーキテクチャ 4bit積算回路の設計方法 Teratail

直列加算器の動作

第6回

Test04 回路を部品化する にがてぶろぐ

回路図 ヘキサドライブ日記

渓鉄 Quartus Iiの使用方法 加算器の作成

情報画像学実験ii 実験1 論理回路

トラ技 年 5 月号に感化されて 4 Bit コンピュータを Mos Fet で製作する Qiita

乗算器 その1 Hackmd

4 N桁の加算

Logisim 全加算器で4bit足し算 Youtube

Fpga入門 正誤表

ピタゴラスイッチもどき式木製4bit加算器 ニコニコ動画

ハードウェア記述言語 その2

Test04 回路を部品化する にがてぶろぐ

Cpuの創りかた 7 加算器を作る Qiita

リレー式 4bit加算器 Youtube

加算器 Wikipedia

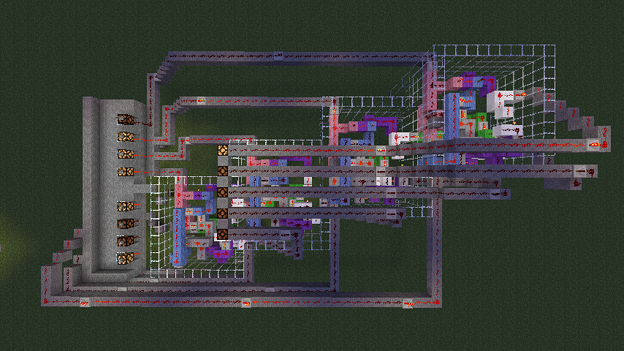

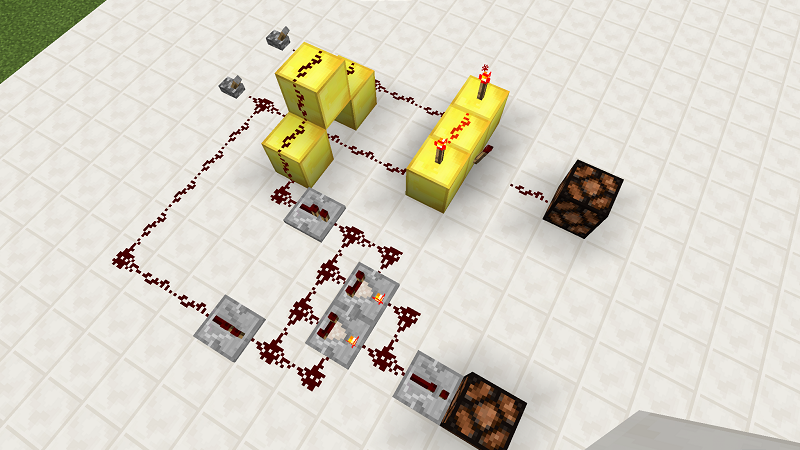

Minecraft 計算機の作り方を分かりやすく解説 半加算器 ナギサものおき

4bit全加算器 Oxygennotincluded Advanced Notes

Carry Lookahead Adder Wikipedia

ハードウェア記述言語 その2

加算器 減算器の原理 制御工学の基礎あれこれ

4bit加算器 株式会社ヘキサドライブ Hexadrive ゲーム制作を中心としたコンテンツクリエイト会社

04 号 加算器 乗算器 及び集積回路 Astamuse

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

Chap9

Ciembor Ciembor 4bit By Ciembor Repository Development Tools Repositories Developers Hub

にがてぶろぐ

問題2 4ビット加算器をverilog Hdlで記述しよう Monoist

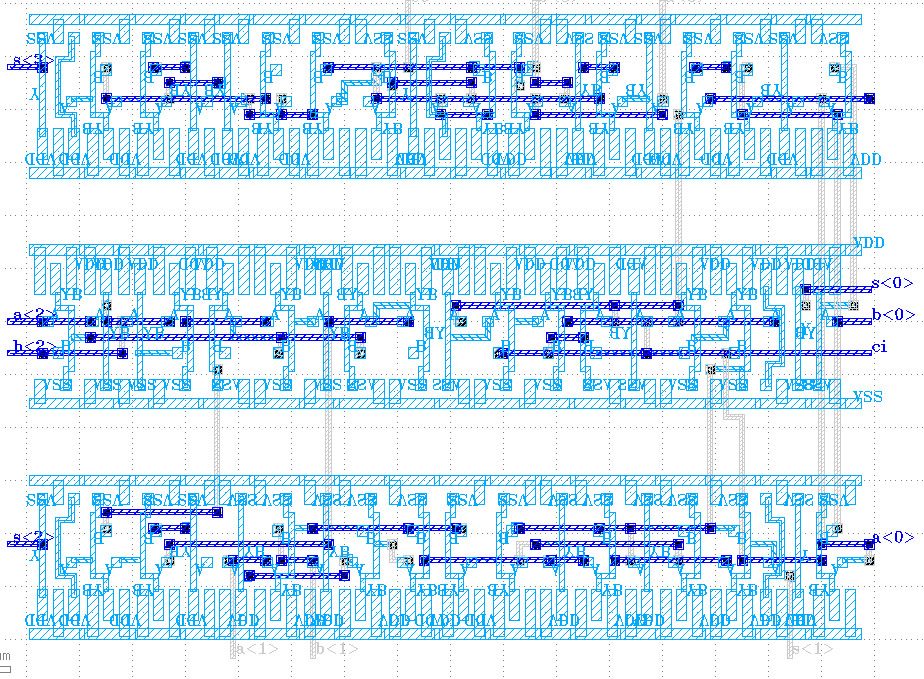

ট ইট র Akita11 Junichiakita Nda不用のopenrule1umスタセル使ってqflowで配置配線 ちょっと大きな回路として4bit加算器 未配線が残ってパラメータを変えて試してるんだけど 行間をあけても どうもそこがうまく使われてない 本来は左右を往来する配線に使

回路図 ヘキサドライブ日記

リレーによる 4bit 加算機

加算器 減算器の原理 制御工学の基礎あれこれ

ttlでcpuを作ろう

4ビット全加算器 水玉製作所

組合せ回路の例 加算回路

加算器 減算器の原理 制御工学の基礎あれこれ

The Strange Storage Zuseの加算回路

4bit加算器 株式会社ヘキサドライブ Hexadrive ゲーム制作を中心としたコンテンツクリエイト会社

4 演算回路の作成

渓鉄 Verilog Hdl記述例 4bit桁上げ伝搬加算器

ハードウェア記述言語 その2

Fpga入門 備忘録 組み合わせ回路編 ハードウェアエンジニアの備忘録

ハードウェア記述言語 その2

4bit全加算器 Oxygennotincluded Advanced Notes

ロボット技術研究会回路講習会17 4

4 演算回路の作成

ハードウェア記述言語 その2

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

全加算器 N Bit加算器 Ushitora Lab

Q Tbn 3aand9gcrmdqitp78vefrypul2k2lazwo Sdcz8vomwa Usqp Cau

Q Tbn 3aand9gctkuhm 1gqj2jysb1aouzjxqzxng1nv7gl8bg Usqp Cau

Computer Archtecture

トラ技 年 5 月号に感化されて 4 Bit コンピュータを Mos Fet で製作する Qiita

リレー式 4bit加算器 ニコニコ動画

半加算器及び全加算器を用いて 4bit二進数のaとbに対し A Yahoo 知恵袋

Retrof

Ltspice 全加算器を作成する Miraiportal

ディジタル電子回路 論理回路のマルチシム

4bit 全加算器 Cmos Dip16 Cd74hc2e 電子部品 半導体通販のマルツ

ハードウェア記述言語 その2

Http Www Ed Noda Tus Ac Jp Jte401 Files 19 Text 2 Pdf